# Les composants électroniques de commutation

## Chapitre IV LE TRANSISTOR MOSFET

### Sommaire

|                                                 |           |

|-------------------------------------------------|-----------|

| <b>1 PRINCIPE.....</b>                          | <b>40</b> |

| 1.1 PRINCIPE DE FONCTIONNEMENT .....            | 41        |

| 1.2 COMPOSANTS PARASITES DU MOSFET.....         | 42        |

| 1.2.1 <i>Les capacités parasites</i> .....      | 42        |

| 1.2.2 <i>La diode parasite</i> .....            | 44        |

| 1.3 AVANTAGES INCONVENIENTS D'UN MOSFET.....    | 45        |

| 1.4 COMPARATIF .....                            | 45        |

| <b>2 COMMUTATION SUR CHARGE RESISTIVE .....</b> | <b>46</b> |

| 2.1 COMMUTATION A LA FERMETURE.....             | 46        |

| 2.2 COMMUTATION A L'OUVERTURE.....              | 47        |

# Les composants électroniques de commutation

## Chapitre IV LE TRANSISTOR MOSFET

### 1 Principe

Le transistor MOS-FET est un transistor à effet de champ (FET=Field Effect Transistor). Il est construit à partir d'un technologie Métal Oxyde et Semic conducteur (MOS). Ce transistor est parcouru par un courant unipolaire (porteurs d'une seule polarité) par opposition au transistor à jonction qui est bipolaire (deux types de porteurs n et p).

Plusieurs types de MOS de "base" existent :

- le MOS à canal P à enrichissement,

- le MOS à canal n à enrichissement,

- le MOS à canal n à appauvrissement ou à déplétion.

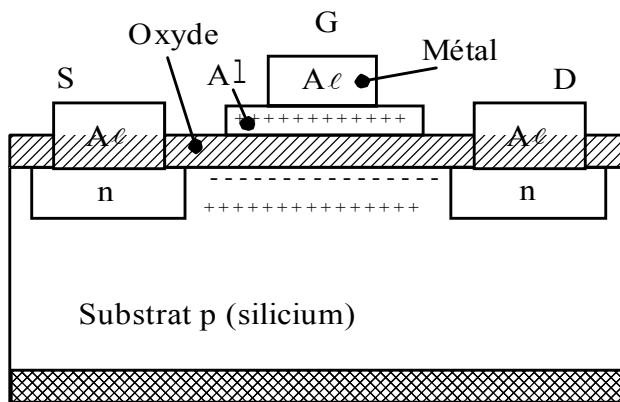

Une coupe schématique de ce dernier est donnée ci-dessous.

Figure 1 : Coupe schématique d'un MOSFET

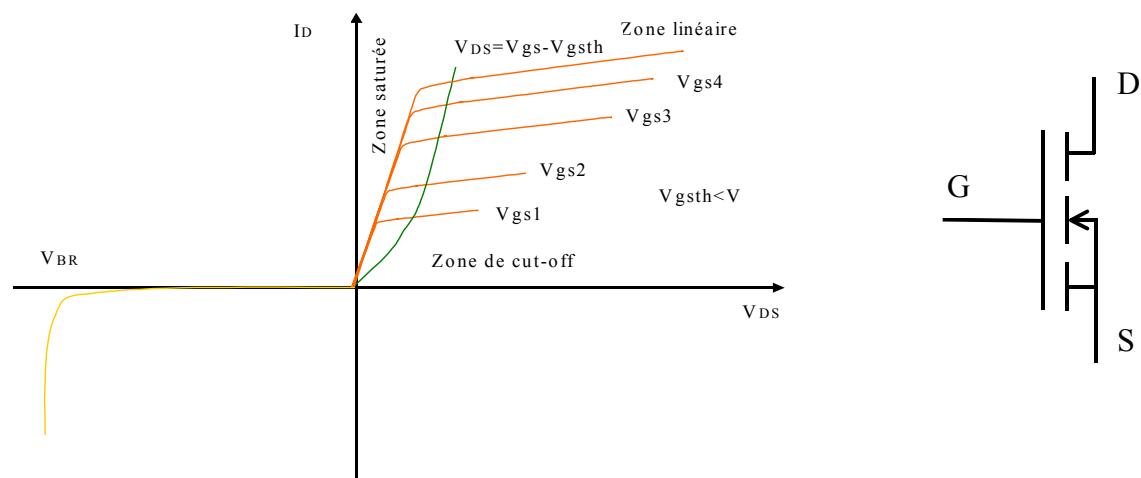

Sa caractéristique statique et son symbole sont portés sur la Figure 2.

*Figure 2 : Caractéristique statique et symbole d'un MOS à canal N à enrichissement*

Remarque : La flèche indique le sens passant de la jonction Substrat-drain.

Un MOS conduit si sa tension  $V_{gs}$  est supérieure à  $V_{gsth}$  (tension de seuil, threshold en anglais). Sur la caractéristique de la Figure 2 on peut voir l'existence d'une zone où le MOS travaille en mode saturé et une zone où il travaille en mode linéaire. La limite entre ces deux zones est une courbe dont l'équation est :  $V_{DS} = V_{gs} - V_{gsth}$ . Si le MOS est polarisé en inverse, seuls les courants de fuite circulent.

On peut remarquer que dans la zone linéaire, le courant n'est pas tout à fait constant pour une tension  $V_{gs}$  donnée. Le courant  $I_D$  croît légèrement quand la tension  $V_{DS}$  augmente. Par conséquent, le MOS ne constitue pas une source de courant parfaite, il présente une résistance de sortie finie. Si on prolonge les courbes de la caractéristique statique du côté des tensions négatives, on se rend compte qu'elles coupent, en théorie, l'axe des abscisses en un seul point  $-\lambda_0$ . Ce point est appelé tension d'EARLY. Cette valeur est toujours approximative et est obtenue en moyennant l'ensemble des résultats trouvés pour plusieurs droites.

## 1.1 PRINCIPE DE FONCTIONNEMENT

La plaquette de silicium est dopée p au tirage, c'est le substrat. La source et le drain sont diffusés avec des impuretés n. La grille est en aluminium, elle est déposée sur l'oxyde ( $\text{SiO}_2$ ) entre drain et source. La face arrière de la plaquette est, elle aussi, métallisée, elle doit être reliée au pôle négatif de l'alimentation tout comme la source. Pour les composants discrets, les constructeurs effectuent en interne la liaison face arrière source. Dans les circuits intégrés, on utilise le substrat, sur une entrée différentielle par exemple, pour équilibrer les MOS grâce à un potentiel variable.

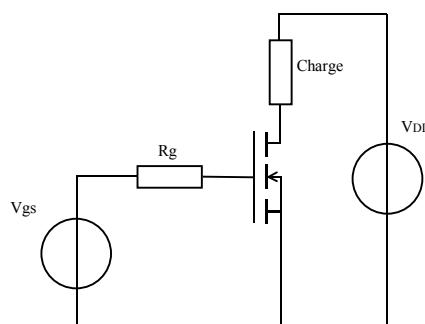

Soit le montage suivant :

*Figure 3 : Montage de base utilisant un MOSFET à canal n*

Si  $V_{gs}$  est nulle ou négative, aucun courant ne circule entre drain et source, car toutes les jonctions pn sont polarisées en inverse.

En appliquant une tension  $V_{gs}$  positive, on crée un champ électrique à la surface du substrat situé entre drain et source qui repousse les trous ou lacunes (positifs) du substrat et attire les électrons (porteurs minoritaires). Si  $V_{gs}$  est supérieure à une tension de seuil  $V_T$  ou  $V_{th}$  (threshold voltage), il y a une inversion de polarité qui crée une zone mince ou canal dopé N qui met en relation, à tra-

vers une résistance  $R_{DSon}$ , le drain et la source. Un courant  $I_D$  prend naissance, il augmente jusqu'à  $I_{Dsat}$  dépendant de  $V_{gs}$  pour une tension  $V_{Dsat}$ .

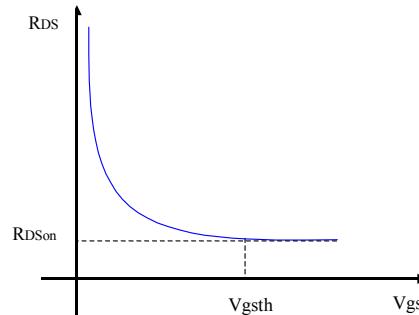

La résistance  $R_{DSon}$  est fonction de l'épaisseur du canal, ou dit autrement  $R_{DSon}$  dépend de la tension  $V_{gs}$ . La caractéristique statique (valable pour de faible variation) de cette résistance de canal peut être représentée de façon simplifiée par le schéma suivant :

Figure 4 : Caractéristique statique simplifiée de  $R_{DSon}$

## 1.2 COMPOSANTS PARASITES DU MOSFET

Tous les composants possèdent des composants parasites, mais en général on les prend en compte que pour des cas bien particuliers. Pour les composants à grille isolée, les effets de certains composants parasites sont visibles quelle que soit l'application. Nous allons donc les définir.

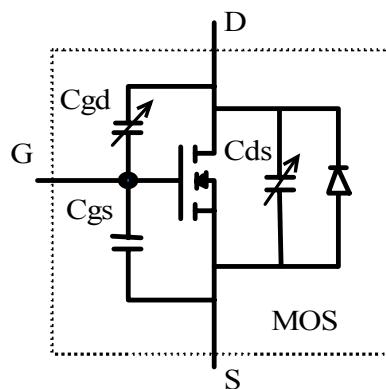

La figure suivante montre le MOSFET et ses composants parasites.

Figure 5 : Le MOSFET et ses composants parasites

Nous avons donc une capacité parasite aux bornes de chaque jonction, plus une diode en antiparallèle sur la jonction drain source.

### 1.2.1 Les capacités parasites

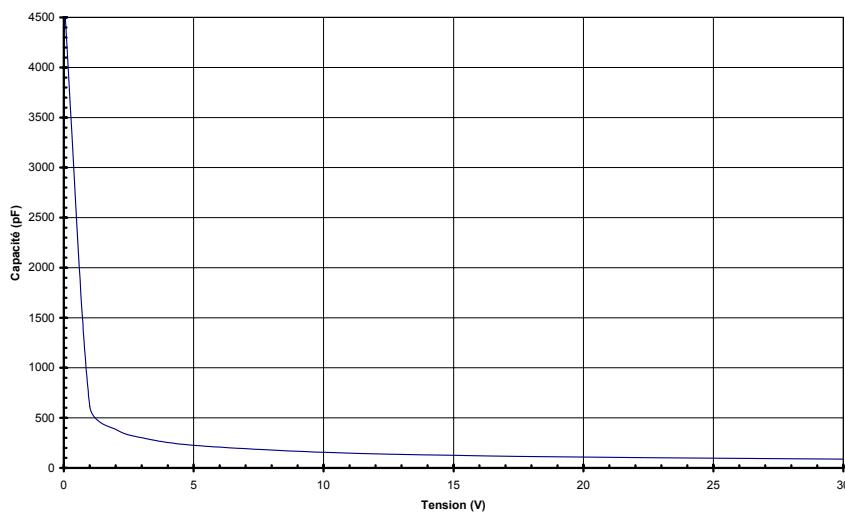

Les capacités sont très peu influencées par la température et la fréquence. Par contre, les capacités grille drain ( $C_{gd}$ ) et drain source ( $C_{ds}$ ) ont une valeur qui dépend de la tension à leurs bornes, alors que la capacité grille source ( $C_{gs}$ ) peut être considérée comme constante.

Les deux premières peuvent être représentées par l'équation de variation des capacités de diffusion<sup>1</sup>, soit :

$$C = \frac{C_{v0}}{(1 + V / \phi_B)^n}$$

Où

$C_{v0}$  est la valeur de la capacité à zéro volts,

$\phi_B$  est le potentiel de jonction,

$V$  est la tension aux bornes de la capacité ( $V > -\phi_B / 2$ ).

$\phi_B$  et n, dépendent du semi-conducteur; pour le silicium respectivement 0,7V et 0,5<sup>2</sup>.

Une simulation de l'équation ci-dessus pour Cgd est donnée Figure 6.

Figure 6 : Variation de la capacité  $C_{gd}$  en fonction de la tension appliquée à ses bornes (MOS Philips PHP6N60).

La grosse difficulté réside dans la mesure des valeurs  $C_{v0}$ . Cela étant, cette mesure est nécessaire pour une bonne simulation, même si les constructeurs fournissent plusieurs données comme :

- la capacité d'entrée  $C_{iss}$ , mesurée entre grille et source, en court-circuitant le drain et la source,

$$C_{iss} = C_{gs} + C_{gd},$$

- la capacité de sortie  $C_{oss}$ , mesurée entre drain et source, en court-circuitant la grille et la source,

$$C_{oss} = C_{ds} + C_{gd}$$

- la capacité de transfert inverse  $C_{rss}$ , mesurée entre drain et grille, avec la source non connectée,

$$C_{rss} = C_{gd}$$

<sup>1</sup> F.-F. Protiva, O. Apeldoorn, N. Groos : « New IGBT model for PSPICE », EPE 1993

<sup>2</sup> Randall L. Geiger, Phillip E. Allen, Noël R. Strader : « VLSI Design Techniques For Analog And Digital Circuits », Mc Graw-Hill International Editions, p 161,162.

On peut donc en déduire :

$$\begin{aligned} C_{gs} &= C_{iss} - C_{rss} \\ C_{ds} &= C_{oss} - C_{rss} \end{aligned}$$

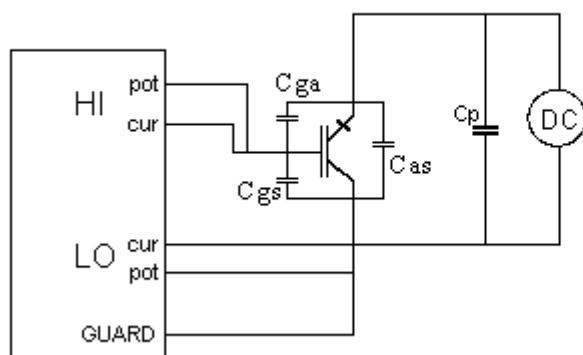

### 1.2.1.1 Principe de mesure des capacités

Pour mesurer de telles capacités, il faut utiliser des analyseurs d'impédance ou pont d'impédance de précision. Ces appareils utilisent une *mesure Kelvin* dite mesure des *quatre points*.

Généralement, les appareils ont soit une amplitude de tension élevée (exemple de  $-200$  à  $+200$ V pour le HP4275A) et un pas de variation, qui dépend d'une source extérieure, assez grand, soit l'inverse (exemple de  $-40$  à  $+40$  V pour le HP4294A).

Le montage est alors du type suivant :

Figure 7 : Principe de mesure de la capacité  $C_{gs}$  pour une valeur de  $V_{DS}$  donnée

Remarques :

La pin GUARD est un potentiel de référence.

La capacité  $C_p$  filtre le signal sinusoïdal provenant de l'analyseur vis-à-vis de la tension continue DC.

Le composant ci-dessus est une combinaison MOS-bipolaire (MBS), mais le principe de mesure reste le même.

### 1.2.2 La diode parasite

La diode parasite va stocker une quantité de charge non négligeable (Cf. cours et TD sur la diode). Par conséquent, elle va notablement ralentir la commutation du MOS. Pire encore, si la pente de tension  $dV_{DS}/dt$  est élevée ( $>qq$  kV/ $\mu$ s) pendant la phase de blocage de la diode, il peut y avoir une destruction du composant.

On cherche donc à éliminer ce composant. Aujourd'hui, la plupart des constructeurs ont intégré une diode en parallèle beaucoup plus performante que la parasite et qui permet le passage de courant pour les charges inductives dans les montages en pont.

### 1.3 AVANTAGES INCONVENIENTS D'UN MOSFET

La tableau ci-dessous donne quelques avantages et inconvénients d'un MOSFET.

| Avantages                                                                                                           | Inconvénients                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>DSon</sub> très grande                                                                                       | Très sensible à la contamination lors de la fabrication                                                                            |

| Impédance d'entrée élevée >100MΩ due à la structure MOS, donc grand en I très élevé (peu de consommation en entrée) | Très sensible aux Décharges ElectroStatiques (ESD), ne jamais laisser la grille en l'air. Mettre une zener entre grille et source. |

| Facile à fabriquer car peu d'opérations                                                                             |                                                                                                                                    |

| Petite surface de silicium                                                                                          | R <sub>DSon</sub> relativement élevée                                                                                              |

| Il est symétrique                                                                                                   |                                                                                                                                    |

| Tension de seuil importante (2,5 à 4V ou 0,8 à 2V)                                                                  |                                                                                                                                    |

| DMOS et VMOS, fréquences de commutation élevée (de l'ordre du GHz)                                                  | MOS, pas très rapide                                                                                                               |

|                                                                                                                     |                                                                                                                                    |

On peut ajouter à cela :

- Le circuit de commande très simple,

- Le MOS supporte très bien la mise en parallèle sans dispositif particulier grâce à son coefficient de température positif. Il s'auto régule, si la température augmente, I<sub>D</sub> diminue et donc la température décroît, etc...

On réalise donc des MOS de puissance en mettant en parallèle de nombreux petits MOS. Les SIPMOS de siemens sont les interfaces entre les circuits intégrés LSI (1mA, 5V) et les charges qui nécessitent de la puissance.

Cela permet également d'obtenir l'image du courant I<sub>D</sub> total en sélectionnant que quelques cellules MOS. Ces transistors sont appelés SENSFET (International Rectifier) et sont très utilisés avec les drivers qui incluent un contrôle du courant (Linear technology).

### 1.4 COMPARATIF

Entre bipolaire et VMOS

|                            | Bipolaire                         | VMOS                               |

|----------------------------|-----------------------------------|------------------------------------|

| Impédance d'entrée (Ω)     | 10 <sup>3</sup> à 10 <sup>5</sup> | 10 <sup>9</sup> à 10 <sup>11</sup> |

| Amplification en puissance | 100 à 200                         | 10 <sup>5</sup> à 10 <sup>6</sup>  |

| t <sub>on</sub> (ns)       | 50 à 500                          | 4                                  |

| t <sub>off</sub> (ns)      | 500 à 2000                        | 4                                  |

| Résistance série (Ω)       | 0,3                               | 3                                  |

Entre plusieurs SIPMOS

| SIPMOS                | BUZ 10     | BUZ 20     | BUZ 30     | BUZ 40    | BUZ 50  |

|-----------------------|------------|------------|------------|-----------|---------|

| V <sub>DS</sub> (V)   | 50         | 100        | 200        | 500       | 1000    |

| I <sub>D</sub> (A)    | 12 à 30    | 8 à 20     | 4,5 à 11   | 1,7 à 7,7 | 2 à 4,2 |

| t <sub>on</sub> (ns)  | 40         | 30         | 100        | 150       | 200     |

| t <sub>off</sub> (ns) | 100        | 95         | 200        | 550       | 600     |

| R <sub>DSon</sub> (Ω) | 0,03 à 0,1 | 0,06 à 0,2 | 0,2 à 0,75 | 0,6 à 4,5 | 2 à 3,5 |

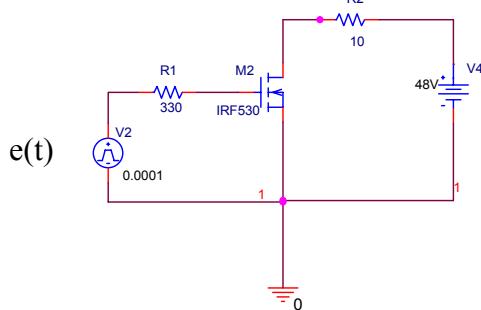

## 2 Commutation sur charge résistive

Soit le montage suivant :

La commande  $e(t)$  est un créneau tension suffisamment long pour que du point de vue de la commutation on puisse le considérer comme un échelon.

La valeur de  $E$  est prise supérieure à  $V_{th}$  de telle sorte que  $R_{DSon}$  soit le plus faible possible.

Figure 8 : Montage utilisé pour l'étude du MOSFET et tension de commande  $e(t)$

### 2.1 COMMUTATION A LA FERMETURE

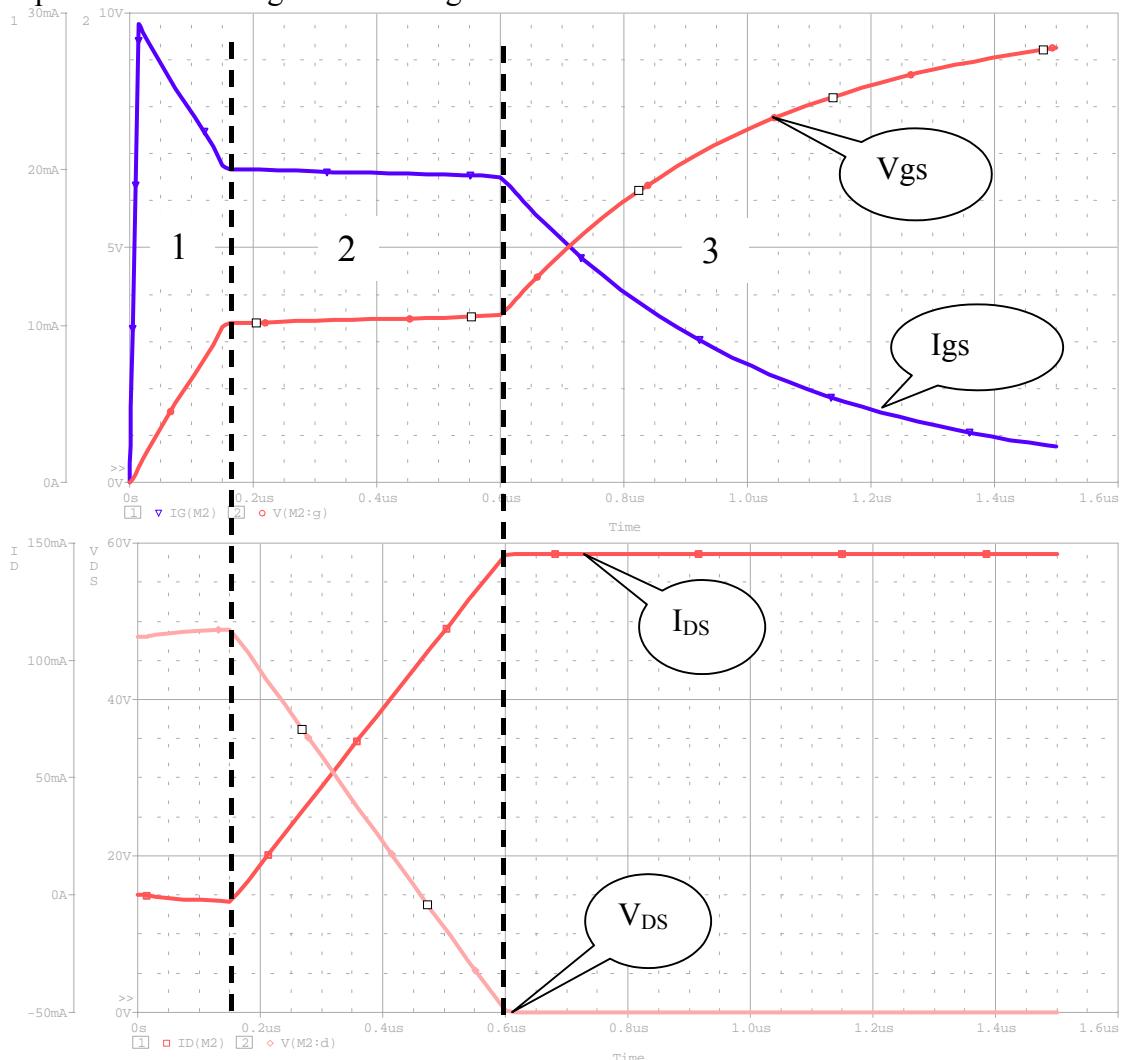

Les tensions et les courants pour la commutation à la fermeture et à l'ouverture sont respectivement représentés sur la Figure 9 et la Figure 10.

Figure 9 : Tension et courant à la commutation à la fermeture du MOSFET

### Phase 1

A  $t=0$ , l'échelon de tension est appliqué sur la grille.  $C_{gs}$  se charge, mais comme  $v_{gs}$  est inférieure à  $V_T$ ,  $i_D$  et  $v_{ds}$  sont pratiquement constants donc  $C_{gd}$  et  $C_{ds}$  aussi. Le transistor est toujours bloqué.

### Phase 2

Maintenant un courant  $i_D$  existe, la tension drain grille diminue, donc  $C_{gd}$  augmente. Cette capacité se charge grâce à un courant d'appel  $i_{C_{gd}} = C_{gd} \frac{dv_{C_{gd}}}{dt}$  ( $\frac{dv_{C_{gd}}}{dt}$  est supposé constant) qui s'oppose à la charge de la capacité  $C_{gs}$  en absorbant la majorité du courant fourni par la commande. Ce qui donne le plateau présent sur la tension de grille du composant. Cette contre réaction entre tensions de collecteur et de grille est connue sous le nom d'effet Miller. On dit par extension que  $C_{gd}$  est une capacité Miller.

### Phase 3

La charge de  $C_{gd}$  est presque terminée et  $v_{gd}$  est pratiquement constante car  $v_{ds}$  devient inférieure à la tension de pincement et donc le transistor entre dans sa phase de saturation.  $C_{gs}$  continue à se charger jusqu'à la tension E en accumulant des charges en excès.

## 2.2 COMMUTATION A L'OUVERTURE

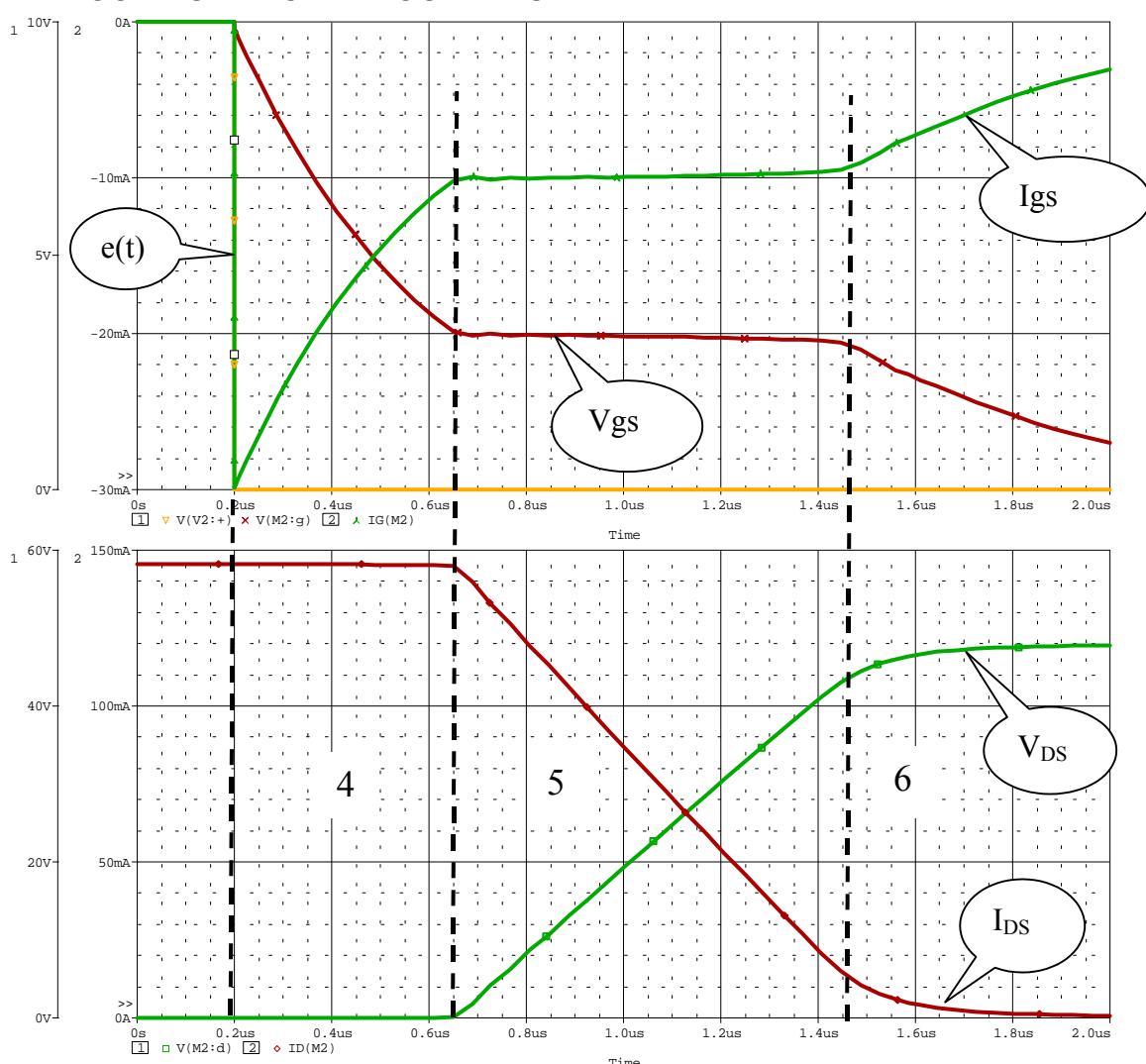

Figure 10 : Tension et courant à la commutation à l'ouverture du MOSFET

Pour la commutation à l'ouverture on trouve les mêmes phases qu'à la fermeture mais en sens inverse.

Phase 4

La capacité  $C_{GS}$  évacue les charges accumulées en excès.

Phase 5

A  $v_{GS} = V_T$ ,  $R_{DSon}$  augmente,  $C_{GD}$  augmente et fournit un courant à  $C_{GS}$  qui provoque le plateau de  $v_{GS}$ .  $I_D$  et  $v_{DS}$  varient.

Phase 6

Quand  $v_{DS}$  atteint la tension d'alimentation  $C_{GD}$  ne fournit plus de charge et on observe une décroissance de  $v_{GS}$  qui correspond à la décharge de  $C_{DS}$ .  $R_{DS}$  est égale à  $R_{DSoff}$ , donc plus de courant  $i_D$ .

Remarque :

Cette commutation à un aspect qui est valable quelle que soit la charges. Cependant quand le transistor est monté dans une cellule de commutation avec une charge inductive et sa diode de roue libre les courbes diffèrent quelque peu. En effet, la montée en courant se fait entre  $V_T$  et un plateau  $v_{GS1}$ , ensuite on a le plateau Miller et seulement la décroissance de  $v_{DS}$  pendant cette phase. Idem à l'ouverture d'abord la montée de la tension puis ensuite la décroissance du courant.

**Note :**

Il existe des transistors qui ont été conçus pour être directement commandés par des signaux logiques TTL (0,+5V). On les nomme L<sup>2</sup>FET (Logic Level gate FET).